# SiRFstar III System Guidelines and Considerations

(For GRF3w Design Related Implementations)

## Document Number: **APNT3001** Revision 1.0 02/05/05

Author: JC Chernicky

#### PROPRIETARY NOTE

This document contains proprietary information to SiRF Technology, Inc. and shall not be reproduced or transferred to other documents or disclosed to others or used for any purpose other than that for which it was obtained without expressed written consent of SiRF Technology, Inc

## SiRFstar III System Guidelines and Considerations

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

(GSP3f) APNT3001 Revision 1.0 2/5/05

#### TABLE OF CONTENTS

| 1 |                                                                                                            |    |

|---|------------------------------------------------------------------------------------------------------------|----|

|   | 1.1. Background                                                                                            | 1  |

| 2 |                                                                                                            |    |

|   | 2.1. Glossary of Special Terms                                                                             | 1  |

|   | 2.2. Industry Standards                                                                                    |    |

|   | 2.3. SiRF Documents                                                                                        |    |

|   | 2.4. Appendices                                                                                            | 2  |

| 3 | The GSP3f Baseband Processor and Interfaces:                                                               |    |

|   | 3.1. GRF3w RF Front End Interface                                                                          |    |

|   | 3.1.1. Reference Clock Changes                                                                             |    |

|   | 3.1.2. AGCDAT                                                                                              |    |

|   | 3.1.3. SPI Interface                                                                                       |    |

|   | 3.1.4. nRESET, SIGN, MAG & CLKACQ                                                                          |    |

|   | 3.2. Block Diagram of GSP3f with GRF3w                                                                     |    |

|   | 3.3. GSP3f Power Requirements                                                                              |    |

|   | 3.4. Pin Definitions and Functionality                                                                     | 7  |

| 4 |                                                                                                            |    |

|   | 4.1. System Operation: Supplemental Comments:                                                              | 9  |

|   | 4.2. RTC Considerations and External Drive Requirements                                                    |    |

|   | 4.2.1. External RTC Drive                                                                                  |    |

|   | 4.2.2. RTC crystal requirements                                                                            |    |

|   | 4.3. Battery Backed Operation for the RTC Cell and Low Hibernation Currents                                | 11 |

|   | 4.4. ECLK Input Characteristics                                                                            | 12 |

|   | 4.5. JTAG Requirements and Considerations                                                                  |    |

|   | 4.5.1. Special JTAG Test Concerns to Remember                                                              |    |

|   | 4.6. External interrupts and nEITx considerations                                                          |    |

|   | 4.6.1. ON_OFF Characteristics                                                                              |    |

|   | 4.6.2. nEIT[0]                                                                                             |    |

|   | 4.7. SPI ports and interface considerations                                                                |    |

|   | 4.8. UARTS                                                                                                 |    |

|   | 4.9. Internally Packaged Flash Considerations                                                              |    |

|   | <ul> <li>4.10. Pre-Flashing of the Internal Flash</li> <li>4.11. Interfacing to External Memory</li> </ul> |    |

|   |                                                                                                            |    |

|   | <ul><li>4.12. Interfacing to External Flash or SRAM</li><li>4.13. Other Functions (and pins)</li></ul>     |    |

|   | 4.14. Watchdog Timer Function                                                                              |    |

|   | 4.14. Valchuog Timer Function                                                                              |    |

|   | 4.16. Interfacing to the RF chip                                                                           |    |

|   | 4.17. GRF3w RF Front End Operation and Interface Considerations                                            |    |

|   | 4.17.1 Power supply requirements, and initial power up considerations for the GRF3w                        |    |

|   | 4.18. RF Considerations with the 3w chip                                                                   |    |

|   | 4.18.1. Internal vs. External LNA in the GRF3w, Filtering and Antennas.                                    |    |

|   | 4.18.2. Allowable LNA gain range and characteristics for the GRF3w part                                    |    |

|   | 4.19. TCXO Considerations (ALL SiRFstar III designs)                                                       |    |

| 5 |                                                                                                            | 20 |

| 6 | 5                                                                                                          |    |

| 0 | 6.1. SiRFLoc Aiding Considerations                                                                         | 20 |

| 7 | •                                                                                                          | 20 |

| 1 | 7.1. Digital and RF Interface Issues:                                                                      | 20 |

|   |                                                                                                            | 29 |

#### SiRFstar III System Guidelines and Considerations (GSP3f) This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

| 7.2.  | SiRFstar III Power Sequencing (in general)                           |    | 29 |

|-------|----------------------------------------------------------------------|----|----|

| 7.3.  | RF Related Jamming and Test Issues                                   |    |    |

| 8.    | Layout Comments and EMI Mitigation                                   |    |    |

| 8.1.  | GSP3f Power Planes, Decoupling and Broadband Noise                   |    | 31 |

| 9.    | Packaging, Assembly and Rework Considerations.                       | 32 |    |

| 10.   | ESD Ratings                                                          | 32 |    |

| 10.1. |                                                                      |    | 32 |

| 11.   | DOCUMENT MAINTENANCE                                                 | 32 |    |

| 11.1. |                                                                      |    | 32 |

| 11.2. | •••••••                                                              |    | 32 |

| 12.   | Appendices                                                           | 33 |    |

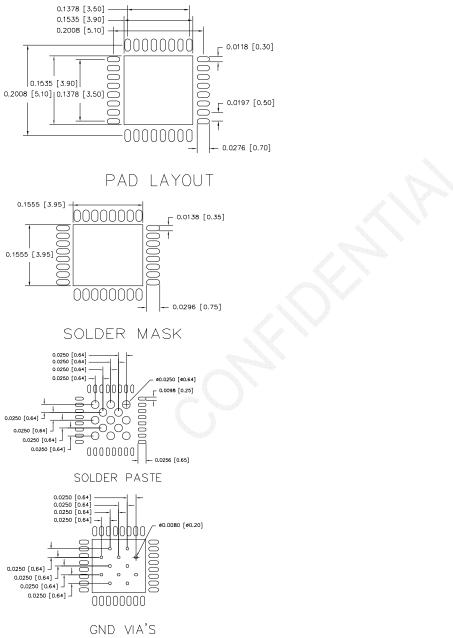

| 12.1. | Appendix A – Recommended Solder Pad Footprints                       |    | 33 |

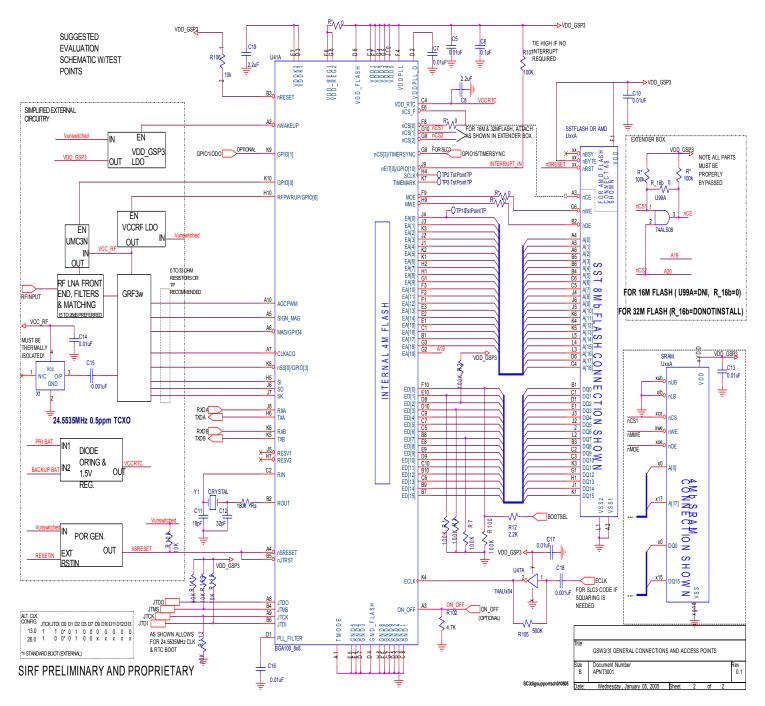

| 12.2. | Appendix B1 – External Memory Interconnect Diagram and Test Circuits |    | 34 |

| 12.3. | + + + · · · · · · · · · · · · · · · · ·                              |    |    |

| 12.4. |                                                                      |    |    |

| 12.5. |                                                                      |    |    |

| 12.6. | Appendix C: Pin Definition Table & Summary                           |    | 40 |

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

## 1. Introduction

This document discusses the suggested system design guidelines and considerations for implementation of the SiRFstar III chipset, hereafter identified as the GSP3f Baseband processor with integrated Flash memory, and the corresponding GRF3w RF front end. This set is considered the first generation of chip options available for the SiRFstar III family of chips. Future generation of chipsets will be discussed in subsequent APNT releases.

## 1.1. Background

The initial focus of this document will center on the GSP3f chip, the pin functionality and the key design considerations. Where possible, attempts to clarify the functionality in autonomous mode and aided mode will be noted. Subsequent sections will discuss the interface to the GRF3w RF chip. In addition, the design implementations and considerations that must be addressed during system configuration and advance planning, front end options and integration/ packaging issues. Radio co-existence considerations will also be partially discussed.

## 2. References

## 2.1. Glossary of Special Terms

**APM:** Advanced Power Management. The mode of low power management used in conjunction with SiRFLoc 3.x software. Update rates are limited from 10 seconds to 255 seconds. The software evaluates the signal environment, and adjusts for full power when needed. <u>Used with SLC3 aided code</u>.

**ATP:** Adaptive Trickle Power mode. The mode of low power operation that intelligently switches between trickle power and full power depending of signal strength to minimized low power operation. Typically defaults to full power operation at signal levels of <28dB Hz. <u>Used with standard GSW3 code</u>.

**BIU:** Bus Interface Unit: Internal controller subsection of the GSP3f.

**FSM:** Finite State Machine: Advances the low power RTC based circuit in certain modes and states.

**GSW3.x:** Autonomous operation software: Term defining standard, autonomous software used for SiRFstarIII receiver operation, version 3.x.

**HIBERNATE STATE:** A very low power standby state under future development by SiRF. Sometimes referred to as "Extreme Low Power". Allows for faster startup during periods of deep sleep.

**SLC3.x:** Aided operation Software: Term defining the operation of aided SiRFLoc Client 3.x software operation with the SiRFstarIII receiver. Also referred to as "Multimode".

**POR:** Power on Reset: An externally generated active low signal used for system reset.

**PTF:** Push-to-FixTM: A power savings mode characterized by infrequent power-on times, and allows for a push button fix in 2 to 8 seconds, on demand.

**RTC:** Real Time Clock: Circuit used to keep current time when the main power to the receiver is off.

**RTCM:** Radio Technical Commission for Maritime Services. A protocol for transfer of differential GPS corrections.

**STANDBY STATE:** (Also called Trickle Power) The mode of power management where the RF power is off (for the 3w) and the Baseband power is ON, but no clock is executing processor activity. This requires about 700uA of current, typically.

#### 2.2. Industry Standards

Additional documents will be referenced at a future time.

#### 2.3. SiRF Documents

APNT 3002: PCB Design Guidelines for SiRFstar III Implementation

APNT 3003: Troubleshooting Notes for SiRFStar III Implementation

APNT 3004: Co-Location and Jamming Considerations for SiRFstar III Implementation

APNT 3005: GPIO Pin Functionality for SiRFstar III Implementation

APNT 3008: Advanced Power Management (APM) Considerations for SiRFstar III

APNT 3009: Production Testing of SSIII Modules

APNT 3012: System Validation Techniques for SSIII.

**APNT 3014:** SiRFLoc Aiding Considerations

GPS Clock Specification for the SSIII System

#### SiRF Reference Design Schematics 1060-0122 and 1060-0122

SiRF SDK Users Guide

SiRFlash 2.14+.

SiRFDemo 3.75+:

#### 2.4. Appendices

Appendix A: Recommended Solder Pad Footprints

Appendix B1: Recommended External SRAM Connections

Appendix B2: B3, Buffers Circuits

Appendix B4: Boot Up Sequences, In Detail.

Appendix C: Special Pin Functions and Cross Reference Table

Appendices A, B and C are noted at the end of this document.

## 3. The GSP3f Baseband Processor and Interfaces:

The GSP3f processor chip integrates an ARM7TDMI CPU, along with 4Mb of internally packaged Flash memory. This is a 20 channel capable receiver with matched filters to offer over 200,000 effective correlators for advanced signal processing which offers excellent improvements in the time to first fix (TTFF), and much lower signal sensitivities.

The high degree of versatility in this chip allows for a wide array of GPS product implementations, and the ability to use the ARM processor for additional non-GPS applications.

The baseband processor structure is somewhat similar to earlier SiRFstarII designs from the standpoint of RTC operation, battery backup requirements, ARM functionality and some GPIO functionality. The details of the actual changes will be outlined in later sections in this document. A primary difference to note here is that the internal DSP core, the RTC state machine and the 4 kbytes of battery backed SRAM (BBRAM) now run at 1.5VDC, instead of the 1.8VDC supply previously required in the 2e/LP chip.

Another key change that has occurred is the elimination of the PECL interfaces for CLK, SIGN and MAG data lines. Therefore, the need for PECLREF is not required. Since the new interfaces are CMOS logic levels typically operating at 2.85V, special care must be taken during the layout to properly isolate and shield these lines. The dV/dt edge rate swings are higher, and the possibility of higher EMI levels should be taken into consideration during layout, and additional system EMI measurements should be verified in each end users platform.

Implementation into the smaller 8x8mm package limits the number of available pins, and has thus limited the direct pin assignment and GPIO availability. Therefore, many functions have become 'shared' functions that are defined during the initial boot sequence. Most of the shared pins default to the GPIO state during bootup. Please refer to Appendix C at the end of this document for pin names and cross functionality. Additional details of the shared GPIO functions can be found in APN3005, GPIO Pin Functionality for SiRFstar III.

#### 3.1. GRF3w RF Front End Interface

It is important to note, that with the GSP3f Baseband engine, many different RF reference clock frequencies can be selected due to the unique fractional-N capabilities available with the GRF3w RF chip. Please note that the GRF3w must be initially programmed into the correct divider configuration by a 3-wire SPI port. This mandates that a stable clock be present to the GSP3f chip from some other source during boot-up to allow for proper GRF3w programming. Initial software releases will allow for a boot from RTC approach, and the choice of various reference clock frequencies can potentially be selected by using the proper resistive pull-ups/downs. Boot from ECLK and other sources are possible, and may be addressed in subsequent software releases. Use of shared clocks for ECLK power management and timing requires advanced planning and development.

## Revision 1.0 2/5/05

#### 3.1.1. Reference Clock Changes

controlled copy,

Document Control.

The GSP3f chip no longer relies on the doubled 49MHz GPSCLK supplied from the RF chip. There is now an internal PLL function to allow for frequency multiplication of the acquisition clock (CLKACQ) supplied from the GRF3w. This provides for more versatility in core processing speed, since the doubler that was available in the previous 2i/LP design, is no longer implemented.

contact

please

This provides the developer more versatility in choices of processing speed vs. power consumption tradeoffs, and will become more evident in later system configurations.

#### 3.1.2. AGCDAT

AGCDAT is driven by AGCPWM and is an input. It is a narrow pulse used to control the gain of the IF AGC loop. It is controlled by a 5 bit word, and is a CMOS level signal relative to VDD.

#### 3.1.3. SPI Interface

The SPI interface is also at CMOS signal level, and is used to program the chip for proper fractional N frequency control, and power management.

#### 3.1.4. nRESET, SIGN, MAG & CLKACQ

The nRESET pin (also referred to as RSTB) is a level sensitive input that is used to put the chip into a standard default state when coming out of a sleep mode. A minimum of 1ms low is required to properly set the default state. The threshold voltages of nRESET are VCC\*0.2 min and VCC\*0.8 max. It is driven by the open drain output of nRESET, and requires a minimum of a 10k pull-up to VCC. The SIGN and MAG outputs are receiver data samples, and are CMOS outputs used to drive the GSP3f chip.

The CLKACQ output is a 16.369MHz CMOS clock output that is the reference for the baseband signal processor. It is derived from the divided LO of the GRF3w fractional N synthesizer. Keep this trace short, clean and well isolated.

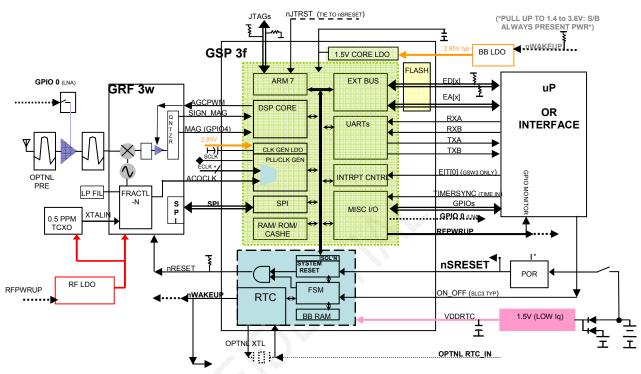

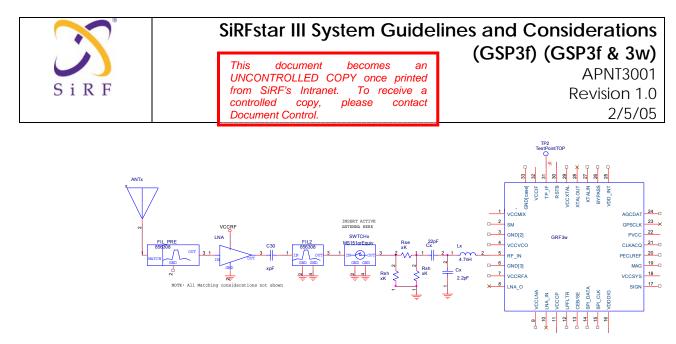

#### 3.2. Block Diagram of GSP3f with GRF3w

A block diagram of the GSP3f chip integrated with the GRF3w chip is shown below.

FUNCTIONAL BLOCK DIAGRAM: 3w + 3f CHIPSET

#### 3.3. GSP3f Power Requirements

Since the GSP3f chip is designed using a lower voltage 0.13um CMOS process, new power supply considerations are in order. For lowest power, the recommended voltage requirements are as follows (-40C to 85C):

| Core Power                                                      | VDDK   | = 1.50V nominal [1]       | (1.40V < VDDK <1.60V) |  |  |  |

|-----------------------------------------------------------------|--------|---------------------------|-----------------------|--|--|--|

| RTC Power                                                       | VDDRTC | c = 1.50V nominal [2]     | (1.40V < VRTC <1.60V) |  |  |  |

| I/O Power                                                       | VDD    | = 2.85V nominal [3]       | (2.70V < VDD <3.60V)  |  |  |  |

| Flash Power                                                     | VDD    | = 2.85V nominal [3, 4, 5] | (2.70V < VDD <3.60V)  |  |  |  |

| Other Power                                                     | VDDx   | = 2.85V nominal [3, 4, 5] | (2.70V < VDD <3.60V)  |  |  |  |

| <b>POWER NOTES</b> : Referenced at 25C, unless otherwise noted. |        |                           |                       |  |  |  |

#### SiRFstar III System Guidelines and Considerations This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact

2/5/05

1. Total receiver power can be expected to run in the ~75mA range (from a 2.85V supply) during the initial acquisition search mode. A peak current surge of 12mA (or more) can also occur during initial acquisitions, and is also a function of the regulators used. This higher current requirement can last from tenths of seconds, to several seconds or more depending on signal strength and accuracy of aiding information. Average tracking current is ~65mA. More information is discussed in separate aiding applications, and power management application note APNT3008. The initial power supply ripple requirements are still TBD, but a reasonably safe value would be ripple for the 3f would be <5mVpp from DC to 3 MHz. EMI issues are still TBD. The RF power must be considerably cleaner, and is discussed later.

Document Control.

- 2. RTC power consists of: a.) RTC clock and state machine operational current, b.) BBRAM power and c.) STANDBY leakage effects. This can be expected to be <10uA during quiescent periods, and \_\_\_\_uA during brief BBRAM read/write operations. This power ring is totally independent of the core power. If one includes the ground pin currents required by the voltage regulators in sleep mode, then this value can be expected to add to the total needed by anywhere from 4uA, to 'x'uA higher. Special considerations relative to transients on this line during battery backup switchover should be minimized as much as possible. VDDRTC voltage ramp time should be <10ms and monotonic, free of any "multi-plateau" characteristics. The initial power supply ripple requirements are still TBD, but a safe value would be ripple of <1mV pp from DC to 3 MHz. A 2.2uF bypass is required on this pin. For additional low power concerns, refer to the special low power APM notes later is this document.

- 3. I/O power has been designed to operate from 2.7V and 3.6V. As of this writing, the GSP3f chip is still not fully evaluated for operation at 2.5V. For all operating conditions and best power /performance tradeoffs, we suggest operation at 2.85V. This I/O power ring is independent of all other power rings. The initial power supply ripple requirements are still TBD, but a reasonably safe value would be ripple of <5mV pp from DC to 3 MHz. Operation at voltages greater than 3.0V are potentially risky, due to the low voltage interface requirements of the new SiRF RF chips. The SiGe process limits the absolute maximum operating voltage of the RF front ends to 3.15V. Therefore, SiRF does not recommend any interface voltage greater than 3.0V for that reason. Use of baseband and RF power supply differences >0.25(TBD) Volts for non 3.3V tolerant inputs could cause latchup effects.

- 4. Flash power is usually in the ~15mA range during read/write. The flash is normally specified for operation down to 2.7V, and timing uncertainties at the lowest voltages is still under characterization. The initial power supply ripple requirements are still TBD, but a safe value would be ripple of <5mV from DC to 3 MHz. SiRF presently cannot guarantee operation for the GSP3f below -40C and at levels less than 2.7V. NOTE: Flash writes occur after a fix has been completed, therefore, the current needed during flash writes, does not affect the peak currents stated above.

INCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control. APNT3001 Revision 1.0 2/5/05

- 5. The internal PLL regulator accepts inputs from 2.45 to 3.6V, and regulates it to 1.5VDC. Operation at the temperatures extremes may introduce some timing problems on a very small percentage of parts when using the minimum of 2.7V. Characterization is in progress. SiRF presently cannot guarantee operation for the GSP3f internal core regulators if the input drops below 2.45V.

- 6. Power supply sequencing: It is important that RTC power is applied first, since the system reset is passed thru this section of the chip first. All remaining GSP3f and GRF3w power should come up at the same time if possible. More details regarding this issue is discussed later in this document.

Higher voltage levels can be used, but will require higher levels of current consumption. This is usually not desirable due to the higher power needed for operation.

Implementation of an external switcher could be considered for core usage to save on battery power, but this has not been fully characterized by SiRF to consider all possible EMI concerns, and thus the client should perform their own validation.

In addition, certain low voltage core GPIO's were designed to be 3.3V tolerant, because they may need to interface to systems requiring higher voltage swings or reference levels.

This information is referenced in APPENDIX C of this document.

#### 3.4. Pin Definitions and Functionality

The shared electrical characteristics and pin functionality is also documented in **Appendix C** at the end of this document. A minimum configuration table for boot from RTC clock, and other clock frequencies, is shown below.

| ED[3] | ED[2] | BOOT CLK      |

|-------|-------|---------------|

| 0     | 1     | =RTCCLK (std) |

| 1     | 0     | =ECLK         |

|       |       | ·             |

| ED[1] | RF Chip Used      |

|-------|-------------------|

| 0     | GRF3w             |

| 1     | ALTERNATE<br>GSC3 |

| ED[0] | Boot Source                |

|-------|----------------------------|

| 0     | External Boot              |

| 1     | Internal Boot (flash load) |

TABLE 3.4.1

## 4. Outline of System Operation with the GRF3w RF Front End

The GSP3f architecture allows for a considerable degree of flexibility in reference clock selection and boot up options. Since the GRF3w RF chip has a Fractional-N synthesizer that is able to accept a clock from 13 MHz to 26 MHz, it is mandatory that the chip be programmed into the proper operating configuration as a primary requirement. This requires an available and known clock source (typically an RTC clock as a default) always be present during the nSRESET high transition to allow for a SPI programming sequence to begin. As previously mentioned, an external clock that is always available could potentially start the process.

For most customers, boot from RTC clock is the typical start up sequence. This requires that the RTC clock circuit be fully operational and stable when coming out of nSRESET. A surface mount RTC crystal should be used with the GSP3f chip, or the RTC reference clock could be provided externally. The RTC drive characteristics are discussed later in this document. Please realize that bootup and subsequent SPI programming sequence from an RTC clock will require slightly longer times than a faster clock could offer. The primary consideration that all customers must characterize is; the time required for the ultra low power RTC circuitry to start up and become stable and useable. At cold or hot temperature extremes, this could take several seconds. SiRF suggests that all customers perform adequate characterization of this phenomenon because it is dependent on several factors: primarily the speed of the initial voltage ramp to the VDDRTC supply (regulator and circuit dependent), gain characteristics of the oscillator cell, input/output capacitance, and the choice of RTC crystal used. Use of an adjustable power on reset (POR) supervisor may be desirable until characterization can determine an average statistical time for clock stability in all conditions. The choice of clock reference frequency and boot options is implemented with external pullup/pull-down resistors on the JTCLK and JTDI lines. This is outlined in TABLE 4.0 below. An x denotes don't care (for reference, an internal 100k pull-up is present for lines 9-13). Please note: This table defaults to RTC clock bootup (per pins ED[2], and ED[3]).

| Boot Clk<br>Freq<br>(MHz) | JTCK | JTDI | ED[13] | ED[12] | ED[11] | ED[10] | ED[9] | ED[7] | ED[3] | ED[2] | ED[1] | ED[0] |

|---------------------------|------|------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|

| 24.5535                   | 0    | 1    | х      | Х      | Х      | Х      | х     | 0     | 0     | 1     | 0     | 0     |

| 13.0000                   | 1    | 1    | 0      | 0      | 0      | 0      | 0     | 0     | 0     | 1     | 0     | 0     |

| 16.3690                   | 0    | 0    | Х      | Х      | Х      | Х      | Х     | 0     | 0     | 1     | 0     | 0     |

| 16.8000                   | 1    | 1    | 0      | 1      | 0      | 1      | 1     | 0     | 0     | 1     | 0     | 0     |

| 19.2000                   | 1    | 1    | 1      | 0      | 0      | 1      | 0     | 0     | 0     | 1     | 0     | 0     |

| 26.0000                   | 1    | 0    | Х      | х      | х      | х      | Х     | 0     | 0     | 1     | 0     | 0     |

#### TABLE 4.0 Bootup Configuration Table

If a customer desires, the alternative to consider is boot from ECLK. This option is supported in the first release of software, but is untested. Since most design implementations will integrate the GSP3f with other radios or subsystems, the possibility

follows:

## SiRFstar III System Guidelines and Considerations (GSP3f) (GSP3f & 3w)

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

of other CMOS available clocks must be evaluated for use. Other clock sources can be chosen for use via the internal "glitchless" mux inside the GSP3f, but these are limited to special applications. YCLK is available for those customers who choose to use alternate clock correction approaches, and are willing to pay slightly extra for a fast TTFF solution. This is addressed in a special white paper available at a later date from SiRF Engineering. A brief discussion of the typical GSP3f + GRF3w RTC based **start up sequence** is as

## (This assumes a 24.5535MHz, 0.5ppm reference TCXO is supplied).

The POR generator output (nSRESET) goes low for ~280ms(TBD) initially [40 stable clock cycles minimum]. All power supplies and clocks should be stabilized.

- 1. nSRESET then transitions high, and all pull-ups/downs are latched into the internal registers of the GSP3f, and the boot clock source and frequency is determined at this point.

- 2. RTC clock is used to initiate the external Flash boot sequence.

- 3. RTC clock is used to program the SPI port of the GRF3w for the right frequency plan. This occurs in less than 150 (TBD)ms.

- 4. The GRF3w fractional N synthesizer has now been properly configured to generate CLKACQ at 16.369MHz, and a brief stabilization time is allowed in the code for synthesizer stability. This is all performed via the SiRF software.

- 5. Once stabilized, the internal 'glichless mux' in the GSP3f allows for a smooth transition from the RTC clock over to CLKACQ via SW instructions.

In future development, alternate clock paths for startup could be implemented. For example, if an external buffer is implemented to drive ECLK, then ECLK can be used to run the GSP3f chip directly, or the internal PLL that runs off of CLKACQ can be selected (via SW) to run the GSP3f chip at alternate frequencies when desired. A more detailed boot sequence is detailed in Appendix B4.

#### 4.1. System Operation: Supplemental Comments:

The GSP3f internal MUX circuitry will first sense if the new clock is present, and is ready and able to allow for a successful transition.

If clock sensing is not successful, the transition handoff does not occur, and the initial clock is continued in use as the reference.

Some comments are in order here to help the user understand other factors of the system operation.

a) System reset (nSRESET) goes low for a minimum of >40bootclk cycles(=TBD)ms, assuming the RTC clock is selected for use via the external pull-up resistors. Initial, first time power-up at hot temperatures may take longer for the RTC clock to stabilize.

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

- b) RF chip reset (nRESET) follows the characteristic of nSRESET, and is delayed approximately 30 ns. This reset is sometimes referred to as "RESETB or RSTB", and is used to reset the 3w chip. It MUST be pulled up to 3V maximum via a 10k resistor. The pull-up power must be present before nSRESET goes high.

- c) nCS[0] drives nCS\_F. Use of a zero ohm resistor between pins E6 and F8 for probing access is highly suggested for troubleshooting purposes.

- d) JTRST is defined as active low, and must be connected to the nSRESET line for proper operation at boot up. The internal flash does not require reset function.

## 4.2. RTC Considerations and External Drive Requirements

The characteristics of the GSP3f internal RTC cell are as follows:

Standard Pierce oscillator cell at 1.5V. No active load bias used.

Gain min=TBD. External 1M feedback not required (internal 5Mohm nominal used).

**RTC NOTE**: The VDDRTC pin MUST be bypassed with 2.2uF minimum for successful operation.

#### 4.2.1. External RTC Drive

If a stable RTC clock can be supplied during startup, then the recommended drive level is into RIN pin is:

(This assumes the elimination of the RTC crystal, and the associated capacitors)

Frequency in =32.768kHz.

Stability =20ppm DeltaF/F or better (less).

Vin = 0 to 1.25V min, 0 to 1.6V max. 40% to 60 % duty cycle. No blocking cap is required. Direct couple to RIN if CMOS driver is used.

VDDRTC power must always be on and stable before any external clock is supplied.

#### 4.2.2. RTC crystal requirements

The parameters of the RTC crystal used should be as follows:

Nominal Values Noted.

Rs =80k. Max =TBD

C1 = 3.3 fF

Cload=10pF

Max drive capability of 0.5uW is suggested.

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

Alternate values of:

Rs=90k ohms

C1 = 2.2 fF

Cload=10pF

Are presently under investigation.

The maximum frequency tolerance allowed is +/-20 ppm, deltaF/F.

Nominal frequency is 32.768kHz with a 180k series drive resistor, and 33pF to ground on this node. The RIN node shall have 18pF to ground. This helps to stabilize the "pull-ability" of the crystal, and the offset ratio tends to help improve the start-up time.

Please note that compact routing of this circuit is highly recommended. The trace capacitance should be as low as possible, and all routing should be well isolated from noisy and high speed lines.

Round can packages are not recommended. SMT packages allow for higher success during reflow and over production volumes.

#### 4.3. Battery Backed Operation for the RTC Cell and Low Hibernation Currents

It is important to note the limitations of the GSP3f chip for low STAND-BY and HIBERNATE currents. Because this is 0.13um technology, the leakage currents are higher, and the ability to integrate a low quiescent current 1.5V RTC regulator into the chip is not possible. The small process technology limits the internal core regulators quiescent current to be in the several hundred uA range.

It is important that customers be aware that an isolation bit in the RTC registers will be set prior to any shutdown into HIBERNATE. This is done with the latest version of software. This will avoid higher levels of leakage currents that could occur. In addition, ALL EXTERNAL SIGNALS are assumed to be disabled, or held low during any long term sleep or 'HIBERNATE' states. Otherwise, poor leakage currents will occur, since our input pins are not failsafe. Inadvertent removal of IO power without setting the isolation bits is ok, if external drive lines are disabled. If the isolation bit is not set, due to inadvertent removal of power, users can expect much higher VDDRTC leakage currents.

When in HIBERNATE, the code picks up from the last know state for faster wakeup operation. The power is always supplied to the input of baseband LDO, and hence the startup is much quicker than would be for a standard startup state. In addition, the need for an nSRESET low pulse of several hundred ms is not required.

Because of the higher quiescent current of the internal regulators, the need to utilize an ultra low quiescent current, *external* 1.5V regulator is recommended for lowest HIBERNATE currents. This can also be integrated with external, low leakage Schottky diodes in an OR'ing circuit that allows the VDDRTC to seamlessly transition back and forth between the main supply and battery backup. The operation of this chip set is to ALWAYS have VDDRTC voltage present and properly backed up. Failure to implement this into your design may result in unspecified behavior. Be advised that certain regulators may incur a poor transient response during backup battery transition. Any transient glitch at VDDRTC should be less than ~20mV (TBD) to avoid odd RTC clock counting.

It is important to note that use of a backup battery will always involve some type of long term, self discharge characteristic. If the VDDRTC supply potential drops below 1.2V, there is a risk that the BBRAM contents may be corrupted, and RTC clocks stop.

SiRF's software uses checksums on data elements stored in the BBRAM, but designers should take care to protect their data as well.

The use of low voltage detect circuits can provide extra security against using any corrupted values, but is less of a concern with the SSIII RTC cell.

The BBSRAM is arranged in 1024x32 cells, and is selectable with provisions for byte lane control, allowing byte, half-word and word access.

#### 4.4. ECLK Input Characteristics

For future reference, the need to supply ECLK with an external reference could be a desirable option. Normally, this is a standard CMOS input of 0 to 2.8V typical swing. The range of allowable input high swings should be greater than  $\sim$ 70% of VDD, and is 3.3V tolerant as a maximum. For booting, the allowable range of input frequencies is 10kHz to 50MHz.

Since the ARM clock is dual edge clocked, it is important to drive this pin with a symmetrical, ~50% duty cycle clock source for initial booting. This symmetry requirement is more critical as the ARM clocking frequency approaches 50MHz. For initial boot frequencies at <25MHz, an estimated safe duty cycle range to assume is between 40% and 60%, since an initial div by 4 is used. Higher boot frequencies should approach 50%. Driving the ECLK input directly with a 1200 mV pp (min.) clipped sinewave at lower frequencies, and a properly centered voltage divider is NOT recommended at this point in time. An external buffer in active bias mode (to square the signal up) is suggested to reduce any design uncertainties when driving ECLK with a somewhat sinusoidal source. Use of single gate AU04 (or similar) type inverter configured in active bias mode will avoid the risk of very low frequency oscillations that can occur with other inverter designs having more than one gate stage per inverter.

If baseband power to the GSP3f is removed such as during HIBERNATE, it is assumed that ANY external drive to the ECLK pin will be disabled, or held low. This is normal design practice. Note: This input pin is not a failsafe pin.

**For SLC3 code**: The ECLK input is also the input pin for **clock correction** used in SLC3.x. The maximum allowable input frequency for clock correction purposes is  $\sim$ 33MHz. Any jitter s/b <+/-500ps on the rising/falling edges this CMOS input. (This implies that any buffer used to drive this pin, be free of excessive noise. Characterization is recommended to verify the jitter level that could occur.) The frequency of this input should preferably be a non integer relationship to the input reference signal at XTALIN. For example, a 26MHz XTALIN frequency, and a 13.0MHz ECLK is a ratio of 2.0. This is not desirable for optimal performance. Ratios like 1.25000, 1.33333, 2.111111, etc, are also NOT desirable. Ratios like 1.25364773 or 2.06593225 etc. are preferred.

Please refer to APNT3014, SiRFLoc Aiding Considerations to better understand the ECLK stability requirements and estimated clock error information needed to support fast TTFF and low C/No acquisition values desired by so many customers. It is **VERY** important to understand and know the estimated *levels of drift* (in ppb/sec) for this reference source, on a continuous basis in order to be able to acquire, integrate and track the ultra low signals below -155dBm (~15dB-Hz).

#### 4.5. JTAG Requirements and Considerations

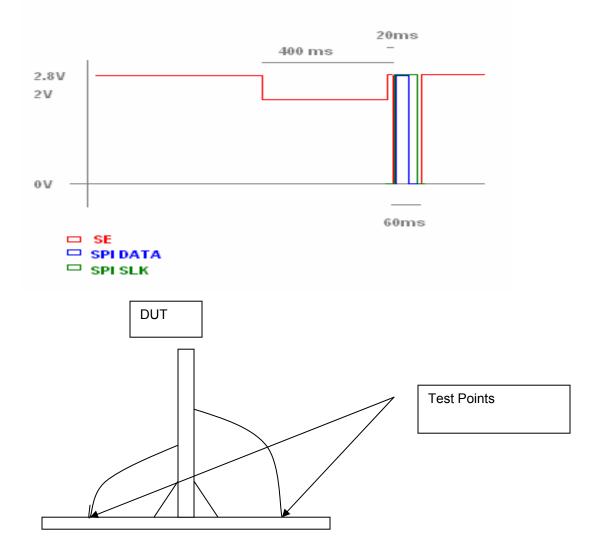

All layouts should allow for some type of JTAG access for system de-bugging possibilities. Dedicated Test Points is the preferred approach.

If this is not possible, allowing for the use of pull up and pull down resistor as access points is acceptable.

JTMS, nJTRST must have 10k pull up resistors. nJTRST must also follow (or be tied to) nSRESET line during the system reset. JTDO is an output, and can float.

JTDI and JTCK define the operational clock source configuration; therefore refer to **Figure 3.2** and **Table 4.0** again for the desired pull up/down frequency selection and boot configurations.

For Multi-ICE testing, the JTDI and JTCK latch registers must be overwritten in order to bring up the chip on Multi-ICE. Pull up/down resistors are highly suggested to assist in module troubleshooting that can be expected.

#### 4.5.1. Special JTAG Test Concerns to Remember

The ARM used in the latest Rev E version of the GSP3f chip has somewhat incompatible HW and SW breakpoints, and is not always repeatable. Please refer to the SDK manual for a workaround solution for this issue.

#### 4.6. External interrupts and nEITx considerations

#### 4.6.1. ON\_OFF Characteristics

- ON\_OFF is designed to be a DIRECT hardware connection to the internal state machine. Activation of this pin is intended to 'wake up' the receiver from a STANDBY state or HIBERNATE (extreme low power) state *only*. To properly implement this when in STANDBY, will require monitoring of the RF supply voltage (level) with an external processors' GPIO pin. For HIBERNATE, RFPWRUP and nWAKEUP must be monitored.

- ON\_OFF should NEVER be used to shut the chip down! In-advertent triggering of this pin while in the fully powered state will cause the chip to crash. There must be an orderly shutdown procedure to properly configuring the isolation register bits. Implementing this monitoring function will also correctly store the BBRAM contents.

- When in HIBERNATE mode, the controlling code must verify that APM is enabled, and verify that all sessions are closed. Note: The controlling code must also allow for a 1 second delay after session is closed, before any attempt to externally awaken the receiver. Refer to the SDK Users Manual for more information. This pin feature for HIBERNATE can ONLY be used with SLC3.1 code and higher.

- If the chip has been externally awakened using the ON\_OFF pin, communication activity must occur within 5 seconds, otherwise, the chip will go back into the sleep mode (this applies to STAND-BY only).

- Since it is a direct link to the core, the use of 3.3V tolerant cells was used in the design of this pin. A 0 to 2.8V CMOS signal is preferred, and is designed to be rising edge triggered, and must stay high a MINIMUM of one full clock cycles of the RTC clock, or ~31us. Use of 2 clock cycles, or 62us minimum allows for a degree of safety margin in the timing budget. This is not a fail safe pin. The 1.5V VDDRTC power should always be on and stable before the signal is asserted. Operation without VDDRTC power is only possible with time aiding. It is still recommended to retain an RTC clock, since network availability is not always possible.

- For GSW3 Autonomous operation, it is suggested to pull the ON\_OFF pin low with a 0 ohm resistor, since interrupts, and HIBERNATE modes are not supported with this code.

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

- For SLC3 aided operation, external wakeups are supported; and this pin should be pulled low with a 4.7k to ~10k resistor, depending on the drive capability of the external driving source. Each rising edge of ON\_OFF advances the state machine, and awakens the receiver. But, as noted above, if incorrectly implemented, this can shut off the receiver when not desired, and lock it up.

- The best way to avoid the lock up concern is to use a GPIO from the external controller, and monitor the voltage level of the VCC\_RF (if low, OK to wake up from the STAND-BY state). This way, a built in system of checks can be implemented in controlling S/W to only enable the ON\_OFF pin when the receiver is in the STAND-BY state. A special external gate may be required for some customer applications. More information on this feature will be supplied in the future.

- If ephemeris is more than 2 hours old, the SLC will request new ephemeris upon wakeup from the network. If the network input is not available, and signal strength is strong enough, the receiver will attempt to automatically collect it from the available satellites.

#### 4.6.2. nEIT[0]

Interrupts can be handled via the EIT pin.

Normally, the user will hold nEIT[0] low until the interrupt is acknowledged by the interrupt handler, and data can be transferred via GPIO pins, or the serial ports.

For GSW3 code, this pin is available for customers to implement an external interrupt WHILE THE RECEIVER IS IN FULL POWER OPERATION ONLY. No wakeup from a HIBERNATE state is possible.

This will require custom software generated (typically by the OEM) with the SiRF SDK Development kit. The pin defaults to active low, and can be configured to be active high via bit 21 of the ASIC\_EIT\_LEVEL register. This is a level triggered signal. It has no internal pullup or pulldown, but most customers will choose to tie high with 100k ohms, and drive with an external source.

In general, this pin is powered from the core voltage (not the RTC), so shutdown of any power to the core will disable this function.

It is also 3.3V tolerant, and could withstand 5V for very short periods. The pulse width is 15ms minimum (TBD).

#### For SLC3 code, this pin is not implemented. Pull high with 0 ohm or 100k

For more information, please refer to the SiRFstarIII SDK Software Reference Manual.

#### 4.7. SPI ports and interface considerations

The GSP3f chip has a muxed SPI port, and is controlled by the two chip select nSS[0] and nSS[1] control pins. At this writing, the SPI port is not available to users. It cannot be used as an alternate UART port, or a comm port. The SPI is a master configuration only, and not able to be configured as a slave. The high degree of multiplexing and interrupts on this pin, and the use of the SPI for RF chip power management control severely limit the use of SPI outside interface with the GSP3f. For reference purposes, the maximum clock speed allowed is ACQCLK/4 or 4MHz at ambient, and nSS[0] is used for RFIC programming, and is not intended for any external use. This becomes evident when one realizes that the SPI ports of the RF chips are not tri-stated after programming, so sharing is not possible.

#### 4.8. UARTS

There are two UARTS available in the GSP3f, designated as UARTA and UARTB.

In GSW3 Autonomous applications, UARTA and UARTB port CANNOT output the same protocol. For example, if UARTA supports NMEA, then UARTB must be set to support SiRF Binary, RTCM or some other user defined protocol. The non standard protocol support capability will occur in later code releases.

In SLC3 aided applications, UARTA uses a channel scheme, and can support any and ALL protocols, while UARTB supports standard SiRF binary or NMEA. Max baud rate is limited to 115kb/sec with this code.

The use of 12 pF output shunt caps is suggested, but not mandatory until further EMI tests are complete. Internal 100k pull-ups are present on the TXA and TXB outputs.

If UARTA is used in an RS485 application, RTS is the output, and CTS is an input.

In future code releases, baud rates approaching 1Mb/sec are possible for flashing only

#### NEMA MESSAGING COMMENTS:

Can I send NMEA for my application while sending SiRFLoc F/AI3 messages to set various setups?

What are the limitations?

A: There are at present, 8 logical channels that a user can open. All of these correspond to the available protocols in the system.

The user will have to open a logical channel to obtain the NMEA. They will also have to strip the SL wrapper before trying to use it with a NMEA piece of equipment. There is one limitation to observe; when operating with multiple logical channels the software will purposely drop non SL message to ensure that all SL message are received/transmitted properly. Refer to the SDK Users Manual for more information.

## 4.9. Internally Packaged Flash Considerations

The internal Flash chip is limited to 4Mbits of memory in a 512kx8 configuration.

The minimum allowable voltage for this chip is 2.7V.

For GSW3 applications, sufficient unused Flash memory exists for outside applications, perhaps 1Mbit (TBD). Adding external flash is possible.

For SLC3 applications, NO FLASH ACCESS IS AVAILABLE FOR USERS.

For proper flashing, use of SiRFlash v2.14 minimum is required.

## 4.10. Pre-Flashing of the Internal Flash

If desired, it is possible to pre-flash the GSP3f chip before assembly operations. This would require a special socket to secure the part, and gain access to the proper CS pins, and ADDRESS/DATA lines. To pre-flash, insert device into socket, apply power, and tie TMODE high to tri state the output pins. (Note: this pin is normally low, or grounded). Then, proceed with standard flash procedures.

Alternately, use of a USB to serial converter, working in conjunction with SiRFlash 2.14 or higher could also be used for flashing at higher baud rates.

## 4.11. Interfacing to External Memory

The GSP3f chip will no longer support 8 bit or 32bit external memory. So use of MUL[0] and MUL[1] is no longer available. The only memory that can be supported is standard 16bit memory.

For this situation the suggested SRAM memory connections should be: pull LB and UB pins low. Then, for any 8-bit access, simply operate on the desired byte. If the user has to have an array of 8-bit values, then a read-modify-write cycle could work (read the existing 16-bit value that contains the desired byte, mask off the byte to change and change it, then rewrite the modified value, changing only the desired byte). This effort may take a bit more code, and may slow down the writing process, but the read will be essentially the same speed, with only the byte extraction process added. The writes can be the same speed if you operate on 2 bytes at a time in appropriate situations.

A sample connection diagram for 16M FLASH and 32M FLASH is shown in Appendix B.

Note: ED7 is different than previous generation chips, and must now be pulled LOW for this chipset when interfacing to 16 bit memory.

## 4.12. Interfacing to External Flash or SRAM

Addition of an external 10k pull-up to VDD on pin G10 (nCS1) of the 3f will be required. This will avoid any 'back-drive' conditions during reset, and is only needed w/external memory.

Customers must realize that there are 2 banks of 16 wide memory, and nCS1 fires the first half of the flash at 41million, and nCS2 fires the second half of the flash at 42 million, so THERE EXISTS A DISCONTINUOUS BOUNDARY to be aware of. This gap in memory could be over 500k, but is compensatable if the proper memory alias is addressed, and the proper bits of the chip select registers are configured. Please refer to the SDK Users Manual for more information.

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

## 4.13. Other Functions (and pins)

[Please refer to **APPENDIX C** for a cross referenced list of all GSP3f pin functions]

**AGCPWM** (multiple use pin: Also noted as GPIO[2]) The typical pulse width is  $\sim$ 11,700ns (bits 11111) at the lowest IF gain, and  $\sim$ 367ns wide (bits 00000) at the highest IF gain. The repetition rate is 1000Hz.

#### nCS[x] Chip Select Considerations:

**nCS[0]** This is the primary external bus chip select pin. The valid address range always starts at address 0x40000000. Has internal pull-up of 100k.

**nCS**[1] (multiple use pin: Also noted as GPIO13, nCTS)

May be used for additional memory devices. The address range is set by chip select registers which also set the read/write characteristics. NOTE: This pin DOES NOT have an internal pullup. An external P/U may be required for external memory due to the flow control in this pin.

**nCS[2]** (multiple use pin: Also noted as GPIO14, nRTS)

May be used for additional memory devices. The address range is set by chip select registers which also set the read/write characteristics. Has internal pull-up of 100k.

**nCS[3]** (multiple use pin: Also noted as GPIO15, YCLK, **TIMERSYNC**)

May be used for additional memory devices. The address range is set by chip select registers which also set the read/write characteristics. Has internal P/U of 100k. Supply the rising edge signal for time aiding to this pin.

**ED**[0:15]. ED[0:15] Memory data lines: Some of these pins are configuration straps that use external pull ups or downs to set internal registers during the reset process.

**GPIO**[0] (multiple use pin: Also noted as REVERSE)

This pin controls an external Darlington transistor switch (UMC3N), which enables power to the external LNA used in the SiRFStarIII design.

Further discussion of power management and related operation and concerns is discussed in the RF front end operation below, and also in APNT3008, Advanced Power Management Considerations.

**GPIO[1]/ODOMETER:** The odometer function is basically a placeholder for future use and evaluation. This block will count rising edges at the ODO pin. The function requires that the high period of the ODO signal be a minimum of one  $\mu$ s long and that the frequency of the clock provided by the clock control block be at least three MHz.

**GPIO COMMENTS:** For GPIO values, port direction and port value assignments for the multi-function GPIO pins, refer to the APNT3005 GPIO Pin Functionality for the SiRFSstar III, or the SiRFstar III SDK Users Guide.

**nMWE** External memory write enable. Active low.

**nMOE** External memory output enable. Active low.

**MUL[0]** This is the lower external 16 bit memory byte select access (lines 0-7). The GSP3f NO LONGER ALLOWS for this control in the present package.

**MUL[1]** This is the upper external 16 bit memory byte select access (lines 8-15). The GSP3f NO LONGER ALLOWS for this option in the present package.

NOTE: SiRFStar III will only support 16 bit interface in little Endian format only. Pull D7 low for 16bit interface. Special code needed to perform word masking if byte transfer is needed. See the SiRFStar III SDK manual for register address and control information.

**PLL\_FILTER** This pin should by bypassed with a nominal 0.01uF capacitor to ground. Use of X7R capacitor material is preferred.

**nRESET** This pin may be used for control of external ICs as well. It can be used to reset the GRF3 SPI block on power up, since nRESET "echos" or follows the nSRESET state (with a slight propagation delay). It is also used to reset the GRF3w logic after power has been removed from the part using nWAKEUP or RFPWRUP to control the corresponding regulator enable pin. nRESET can also be used to control the outputs on an external flash memory that continues to be powered during power down operations. It can control the output state of an external RAM that continues to be powered during power down states, as may be the case for applications requiring additional non-volatile RAM.

Internally, this is an open drain, so an external pullup (recommended value: 10 k $\Omega$ ) is required for proper operation. The open-drain circuit can tolerate up to 3.6 V pullup voltage, but the GRF3w can only tolerate 3.0 V, so we recommend that you limit the voltage on the pullup to VDDRF or 3.0 V, whichever is lower..

**nSRESET** This is the primary system reset for the ARM and internal core. Active low. nJTRST (JTAG reset input) must also be tied to this pin. **Once system boot clocks have stabilized**, hold low for a minimum of 40 clock cycles. The external power on reset generator (POR) circuit supply and the output pullup must be tied to an always present power source. Internal flash does not need a nSRESET connection. *Therefore, do not tie this to the VDDBB if Advanced Power Management or hibernation is used.*

**RFPWRUP** (multiple use pin: Also noted as **GPIO[8]**) This is an active high output, and enables the regulator that powers the GRF3w and is used for power control of the RFIC. Since the RF chip requires SPI programming, power is enabled first, before programming can occur. The default output is high at reset, connected to and controlled by the Finite State Machine.

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

When configured as a GPIO, the only available functions are output and high impedance; there is no input function available on this pin. This pin does not have a pullup or pulldown resistor internally – any desired pullup or pulldown resistor must be supplied externally.

**SCLK** This output is for external synchronous memory, and can output the system clock up to 50MHz for monitoring purposes at CMOS levels. Typically, this will include 7 wait states, depending on the version of code. This is also an available output port that can supply a divided ECLK or BCLK output (BCLK is the ARM clock). The max divider ration can be programmed to 2 <sup>16</sup>-1 Test point access is highly recommended during layout.

**SIGN\_MAG** The SIGN\_MAG input pin allows for special demuxing of a serial and combined SIGN and MAG serial data stream in future designs. In the situation of use with the GRF3w, the SIGN output connects with SIGN\_MAG input of the GSP3f, and the MAG output of the GRF3w connects to GPIO[4] input of the GSP3f. Test point access for these signals **is highly recommended**.

**SI** SPI INPUT data pin The SPI interface with the GRF3w is unidirectional and therefore the SPI input signal is not available to use. Also a GPIO function.

SO SPI OUTPUT data pin. Also a GPIO function.

SK SPI CLOCK pin. Also a GPIO function.

**TIMEMARK** (multiple use pin: Also noted as **GPIO**[9])

This pin provides the 1pps output desired for certain applications. This is a CMOS level output. This function is available with an approximate accuracy of +/-35ns, but could be as high as +-100ns over all conditions and temperatures. The rising edge is synched to the GPS Epoch.

**TIMERSYNC** (multiple use pin: Also noted as nCS3, GPIO[15], YCLK)

This pin is used for time transfer information into the SiRRstarIII receiver with SLC3 code ONLY, and also for alternate applications. When use as a TIMERSYNC input, this input pulse is rising edge triggered, and must be 123ns wide as a minimum, and 1ms wide as an approximate maximum.

**TMODE** This pin must always be pulled low or shorted to gnd. It is used for special factory ATE testing.

**INTERNAL FLASH:** The internally packaged Flash is a SST 39VF400A part, and is arranged in a 256x16 configuration.

#### 4.14. Watchdog Timer Function

The watchdog timer provides a mechanism to detect and recover from unexpected software or system behavior. The watchdog operates by requiring SW to periodically acknowledge an interrupt. If the acknowledgement does not occur, the watchdog self-times out, and initiates a S/W system reset. A flag set in the watchdog registers allows SW to know that

the reset was caused by the watchdog, so that appropriate recovery or notification of the event can be attempted. More information can be found in the SDK Users Guide.

#### 4.15. Special Advanced Power Management (APM) Considerations and Control Pins

**nWAKEUP**: As previously noted, this output pin must be pulled up via a 100k resistor, **to** an always present and continuously "on" or non switched voltage source! Do not tie this pin to the regulated BB power. The pull-up supply voltage must never exceed 3.6V, including transients. The maximum allowable sink current for this pin is 1mA over temperature.

For proper isolation of the chip circuitry, the software configurable isolation bits in the RTC control register (0x80040018) MUST be enabled first, before the chip is put into any long term sleep or hibernate mode. In addition, if placing the GSP3f chip into a long term hibernate state, it is initially suggested that any driving I/O from outside sources or processors be disabled, or preset to a low state. This includes ECLK, TIMERSYNC, RXx, TIMEMARK (in certain situations) and other GPIOs if special S/W is implemented. Inadvertent removal of power could induce odd leakage characteristics if external drive is not disabled. Retaining power to nWAKEUP, nRESET and VDDRTC is acceptable.

#### 4.16. Interfacing to the RF chip

A primary concern when interfacing the RF front end outputs to the GSP3f baseband processor is signal integrity and noise.

For EMI purposes and current consumption reasons, the drivers for the RF chip are not high current drivers. If an end user desires to run the outputs of the RF chip (SIGN, MAG, CLKACQ, AGCPWM) through a high density connector, and with long trace runs, then problems can (and will) be anticipated.

SiRF suggests that the interconnect length for these CMOS buffers be kept under 1 inch, (2.5cm) when possible. **Running these signals through a connector is NOT recommended**, unless proper characterization is performed in advance of initial layout.

Use of source termination resistors may help to improve the ringing that can be associated with CMOS drivers. Therefore, adding 27 to 33 (TBD) ohm series resistors within 5mm of the OUTPUTS of the RF chip will usually improve the driving source characteristics, assuming a 50 ohm trace is used. Allowing for these resistors is HIGHLY recommended for probing and test access, when needed. These resistors could always be replaced with 0 ohm resistors if needed. If no resistors are used, adequate test access to these lines should always be allowed.

All clock lines, and high speed lines, should always have a minimum of three trace widths separation between potential offending lines. Adding a well grounded isolation trace between these traces will also help with noise reduction. Additional suggestions can be found in APNT3002, PCB Design Guidelines for SiRFstar III Implementation.

Since many of the pins are dual use, it is important to realize that the RF chip SIGN output will go into the GSP3f SIGN\_MAG input. The MAG output of the RF chip will go into the nSS[1]/GPIO[4] input pin when the GRF3w is used. AGCPWM (also noted as GPIO[2] will be used to drive the AGC control for the IF section.

#### 4.17. GRF3w RF Front End Operation and Interface Considerations

## 4.17.1. Power supply requirements, and initial power up considerations for the GRF3w

The GRF3w is designed for 2.7V to 3.0V operation. Current consumption in full power mode, with the LNA and TCXO can be expected to average about ~33mA [TBD] at 2.85V. This is the preferred operating voltage for the GRF3w chip. This is also the preferred voltage for the TCXO. The ripple and noise requirements should be as low as possible, since the TCXO typically runs off the RF supply. Power supply noise and ripple from DC to 3MHz is still TBD, but a safe value to strive for would <40uV max. The lowest noise possible, the better. If TCXO power is shared with the GRF3w, it is important to choose a regulator with ~1mV voltage change per degree C for best, low level sensitivity while in a thermally dynamic environment.

The GRF3w is a SiGe chip with extremely high gain. Integrated into this chip is a fractional N synthesizer that allows the user extreme versatility in the choice of reference clock that could be used. The chip is packaged in a 5x5mm QFN32 package. See Appendix A for the suggested solder pad footprint.

This RF chip was originally designed for a standard default reference clock frequency of 16.800MHz, and was designed for SiRFstar II and III applications. If a user selects this frequency, the chip will power up and synthesize the necessary 16.369MHz output out of the fractional N synthesizer after the Fractional-N reconversion, but with PECL output drivers enabled. Therefore, SPI re-programming will still be required to reconfigure to CMOS output drivers.

Since this chip is SiGe, it is extremely important to not exceed the absolute maximum voltage requirements for this part, which is 3.15V. SiRF does not recommend operation above 3.0V.

The maximum allowable VDDBB to VCCRF interface voltage difference is 0.25 (TBD) VDC.

NOTE: Use of ESD protective garments and adhering to strict ESD handling procedures is highly recommended when working with these parts.

In addition, advance planning of HBM ESD related concerns MUST be properly considered and addressed for those customers that have risk areas. The weak areas of ESD sensitivity are SAW filters, RF inputs; LNA's and associated RF sections.

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

#### 4.18. RF Considerations with the 3w chip

#### 4.18.1. Internal vs. External LNA in the GRF3w, Filtering and Antennas.

Although the GRF3w does contain an integrated LNA, SiRF has chosen not to use this in any reference designs. The performance of this chip function is not as advantageous as what can be achieved with an external LNA. An external LNA will offer much superior performance.

Many customers ask about RF front end design: When do we need an LNA? What type of LNA? Do I need a prefilter? What kind of post filters should be used?

These questions are common, and the following rule of thumb should apply:

a) A GOOD antenna and LNA will ALWAYS be required to achieve the desired performance. The antenna and the TCXO are the most critical items for successful GPS reception in a weak signal environment. Proper choice and placement of the antenna will ensure that satellites at all elevations can be seen, and therefore, accurate fix measurements are obtained. Most customers contract with antenna design houses to properly measure the radiation pattern of the final mounted configuration in a plastic housing with associated components near the antenna. Linear antennas are becoming more popular, and the gain is reasonable, since a smaller ground plane can be used. Choose a linear antenna with a reasonably uniform hemispherical gain pattern of >-4dBi. Use of an antenna with lower gain than this will give less than desirable results. Please note that a RHCP antenna with a gain of -3dBic, equates to the same gain achieved with a linear polarized antenna of -0dBi.

Proper ground plane sizing is a critical consideration for small GPS antennas. Therefore, proper placement of the GPS antenna and TCXO should always be the FIRST considerations in integrating a GPS layout. The best implementation possible occurs with proper antenna planning!

- b) Prefilter: If the unit is a stand-alone receiver, with minimal outside interference, and the typical operating environment is free of harmonics and spurious energy in the 1575.42 MHz +/-6MHz band, then a prefilter is not suggested. It will degrade the overall noise figure, adds to the cost, and complicates the front end matching. If integrating into a handset, or multiple radio devices, the use of a prefilter is suggested for best performance. Extreme care must be exercised in the choice of the prefilter used. If this is a SAW device, mismatch effects will increase the insertion loss, and add to the front end noise figure. Close attention to source and load matching is very important, since poor source and load return loss will increase the filter insertion loss, and degrade the amount of rejection possible. Periodic sampling of production lots to validate matching in high volume production is suggested.

- c) The post filter will offer the best rejection opportunity before the signal goes thru the necessary signal processing. The higher the ultimate rejection, the

This document becomes an UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a controlled copy, please contact Document Control.

APNT3001 Revision 1.0 2/5/05

better the anticipated performance. A SAW with an insertion loss of <2.4dB and rejection of >=38dB at +/- 75MHz offset is the minimum suggested rejection. The higher the rejection, the higher the probability of mitigating any potential interference problems. A good rejection peak at 1650MHz also helps in rejecting any PA harmonics. Once again, good source and load matching provides for a more repeatable SAW insertion loss, and rejection characteristic. If the gain of the LNA is high enough, use of a resistive -2dB or -3dB pad after the post filter and before RFIN is a good position, and will help to improve the matching concerns.

d) The Fractional N loop filter BW is slightly greater than 100kHz.

#### 4.18.2. Allowable LNA gain range and characteristics for the GRF3w part

SiRF recommends that the range of TOTAL LNA gain before the RFIN pin of the GRF3w be between the ranges of **12.0dB minimum and 26.0dB as a maximum.** This estimate includes all cable and filters losses, and assumes an antenna with gain of 0dB+/-approximately 3dB. In past designs, some customers chose to implement an external active antenna, in front of the primary and integrated LNA. This could occur, but SiRF does NOT recommend this approach. It will not improve the sensitivity of the total receiver chain. If an improvement is observed, it is most likely due to the improved antenna gain characteristics that can be obtained with an external antenna. Adding this extra gain will cause overdrive issues in the IF section and the quantizers, resulting in reduced quantizer performance. It can also contribute to significantly reduce jamming resistance in the presence of an in-band, or near band interferer, depending on the gain characteristics of the active antenna and subsequent RF chain.

The LNA noise figure should be as low as possible (target <1.5dB) but slightly higher noise figures are allowed if the input and output return loss characteristics of the LNA are better than 15dB. This will help to improve filter characteristics, and reduce total mismatch loss. Use of high Q (>50 or 60) inductors on the series input matching is always suggested. Lower Q (<20) inductors on the output may help to improve output matching. Use inductors and matching caps with 2% tolerances for enhanced unit to unit repeatability.

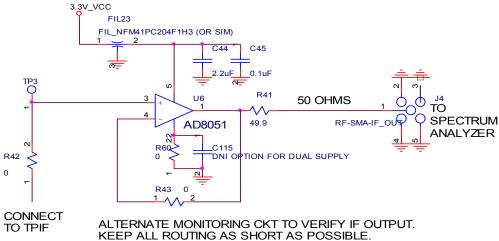

A suggested example schematic of an external active antenna connection node to bypass the internal LNA is shown in Figure 5 below. The use of an optional pi pad can help the amplifier stability, and SAW filter response characteristics. This assumes the amplifier has a gain of at least 17dB for a -2dB pad, or 18dB for a -3dB pad. Ideally, the RF power must be disabled to the LNA not in use.

FIGURE 5: Active Antenna Injection Point

The LNA -1dB compression point should be as high as possible, especially in a highly integrated handset platform. Unfortunately, the higher current draw associated with a higher P1dB LNA is not desirable for battery life. So, compromises can be expected to occur. Usually, a -1dBout compression point of 0dBm can be adequate, if proper PA notch filtering and good isolation techniques are implemented.

Extreme caution should be exercised in the layout of a GPS LNA section, since the probability of oscillations anywhere from  $\sim 100$ kHz to 11GHz can exist. All finished RF layouts should be totally scrutinized for stable operation under all source and load conditions up to 12 GHz minimum.

## 4.19. TCXO Considerations (ALL SiRFstar III designs)

The TCXO requirement for SiRFstar III chipset are considerably much more demanding than previous generation receiver requirements and is discussed below.

When acquiring and tracking deep space satellite signals at very weak levels, oscillator stability is extremely CRITICAL! This cannot be emphasized enough.

Choosing an inexpensive TCXO with this receiver is comparable to running a high performance race car with diesel fuel. The desired results will NOT be obtained.

SiRF recommends (at a minimum) the use of a 0.5ppm temperature stability TCXO that meets all the requirements noted in the SiRF document: GPS Clock Specification for the SSIII System, July 2004 or later.

There are many parameters that are critical requirements that must be met. Phase noise, frequency ramping, thermal gradients, aging, g-sensitivity, frequency micro-jumps, etc., can all affect the ultra low signal acquisition and tracking performance of this deep space receiver. If you are unfamiliar with these requirements, contact your SiRF representative for a copy of this document if you require a more detailed understanding.

#### SiRFstar III System Guidelines and Considerations (GSP3f) (GSP3f & 3w) This document becomes an APNT3001 UNCONTROLLED COPY once printed from SiRF's Intranet. To receive a Revision 1.0 controlled copy, please contact Document Control. 2/5/05

**TCXO NOTE:** Use of a crystal for an oscillator is not recommended, nor is it a cost effective option. The desired low signal sensitivity will not be achieved unless the proper TCXO is used.

It is also extremely important to plan well in advance the proper placement of the TCXO for the lowest exposure to thermal gradient and ramping situations. The primary cause of poor performance in a highly integrated GPS receiver is thermal ramping of the quartz blank inside the TCXO. SiRF recommends that any heat source such as an IC or regulator be located far away from the TCXO. In addition, the use of a cover for the TCXO is also highly recommended for best performance. An excessive thermal ramp rate of tens of millidegrees per second can cause tracking problems. Smaller TCXO's appear to exhibit a higher degree of sensitivity to thermal transients, due to the ultra low thermal mass that these parts exhibit. Use of ultra small TCXO's should be fully characterized before design implementation.

The power supply voltage for the TCXO should also be extremely quiet and stable over the full temperature range. Supply voltage deviations of +/-0.5% from -40C to 85C should be considered the approximate maximum allowable change allowed! A 0.3ppm over the -20C to 70C range is suggested. Most TCXO's are designed for proper operation with a 2.85V supply, and a stable load of 10k ohms in parallel with 10pF. An alternate terminating load for the TCXO could be 20k ohms in parallel with 5pF. The GRF3w will come close to this value, but the resistive term will vary over temperature and from unit to unit. Although not required, adding an optional 75k resistor in parallel with the XTALIN pin will help to stabilize the impedance of this pin slightly. The input Z of this pin appears as a series combination of ~110 ohms in series with 170nH at 2.85V. The shunt equivalent is much higher.

The use of filters on the output of the TCXO is not mandatory, since a doubler is not used.

The minimum input swing required by the GRF3w is 200mVpp over all temperatures, and the absolute maximum allowed is 1200mV pp with a 1000pF ac coupling cap. Exceeding this can overdrive the linearity of the input, and damage the ESD protection diodes on the input of the chip.

Locating the TCXO in a thermally benign area like behind the keypad is suggested, but careful routing of the TCXO clock to the critical sections will be required, and any noise coupling must be non existent.

NOTE: Deviation from the recommended TCXO can result in poor, weak signal acquisition or tracking performance. There are many parameters involved that contribute to the high level of frequency stability required by the SiRFstar III chipset. Use of alternate TCXO's or power supplies for the TCXO, not recommended in our reference designs, will require that the customer perform an EXTENSIVE amount of additional testing to validate the TTFF and system sensitivity under various operating conditions in the final integrated product. This also includes the vibration and handling related oscillator stability concerns. This is due to issues such as quartz crystal mounting, design of the compensation ICs inside the TCXO, internal regulation inside of the TCXO, etc. This extra testing should not be viewed a trivial effort!

## 5. System Operation with Alternate RF Front Ends

This section is left blank for this revision, and will be discussed in more detail in subsequent application notes. Alternate SiRF RF front ends can be used to interface to the GSP3f.

## 6. Weak Signal Acquisition Considerations

It is important to note some general concerns about acquiring weak signals with the SiRFstar III chipset.

For the lowest sensitivities, in the order of 15dB-Hz to 30dB-Hz, longer integration times WILL be required. At present, the SiRFstar III code allows for up to 900ms integration times, and longer shutdown times. In this weak signal mode of operation, position update rates of 2 to 5 seconds is the best that can be expected.